W9751G6NB-25I存储器集成电路(IC)-型号参数

技术参数

| 品牌: | WINBOND华邦 |

| 型号: | W9751G6NB25I |

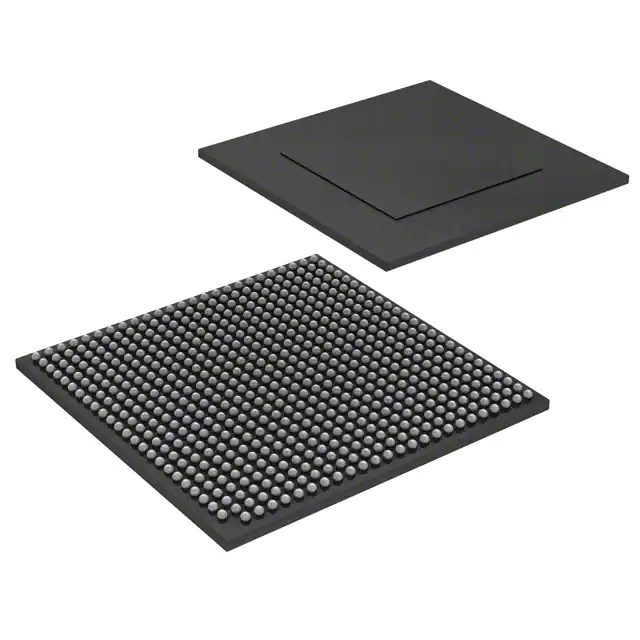

| 封装: | VFBGA84 |

| 批号: | 20+ |

| 数量: | 1 |

| RoHS: | 是 |

| 产品种类: | 电子元器件 |

| 最小工作温度: | -10C |

| 最大工作温度: | 130C |

| 最小电源电压: | 3V |

| 最大电源电压: | 6V |

| 长度: | 6.3mm |

| 宽度: | 7.4mm |

| 高度: | 2.8mm |

1.一般说明:

W9751G6NB是一个512M位DDR2 SDRAM,组织为8388608个字x 4个存储体x 16位。该设备可实现高达1066Mbps(DDR2-106)的高速传输速率,适用于各种应用。W9751G6NB分为以下速度等级:-18、-25、-3、181、251、-31、18J、25和-3J。-18,18l和18J级零件符合DDR2-1066(7-7-7)规范(181工业级,保证支持-40”C S TCASE S 95”C,18J工业级,确保支持-40”S TCASE S 105C)。-25、251和25J级零件满足DDR2-800(5-5-5)或DDR2-800(251工业级,保证支持-40“C S TCASE S 95’C,25工业级以上,保证支持-40*C S TCASES 105C)。-3、-3l和-3J级零件符合DDR2-867(5-5-5)规范(-3l工业级,确保支持-40”C S TCASE S 95‘C,-3J工业级,保障支持-40”C S TCASE S 105C)。所有的控制和地址输入都与一对外部提供的差分锁同步。输入被锁存在差分时钟的交叉点(CLK上升和CLK下降)。所有/O都以源同步方式与单端DOS或差分DQS-bos对同步。

2.特点

- 电源:VDD,VDDQ=1.8V±0.1V

- 双数据速率架构:每个时钟周期两次数据传输

- CAS延迟:3、4、5、6和7

- 突发长度:4和8

- 双向差分数据选通管(DQS和数据质量标准)与数据一起发送/接收

- 边缘与读取数据对齐,中心与写入数据对齐

- DLL将DQ和DQS转换与时钟对齐

- 差分时钟输入(CLK和CLK公司)

- 写入数据的数据掩码(DM)

- 在每个正CLK边、数据和数据掩码上输入的命令都引用到两条边DQS的

- 已发布CAS

- 支持可编程附加延迟以提高命令和数据总线的效率

- 读取延迟=附加延迟加上CAS延迟(RL=AL+CL)

- 芯片外驱动器阻抗调节(OCD)和芯片内端接(ODT),以获得更好的信号质量

- 读取和写入突发的自动预充电操作

- 自动刷新和自刷新模式

- 预充电断电和主动断电

- 写入数据掩码

- 写入延迟=读取延迟-1(WL=RL-1)

- 接口:SSTL_18

- 采用VFBGA 84球(8x12.5 mm2.厚度1.0 mm)封装,采用无铅材料符合RoHS