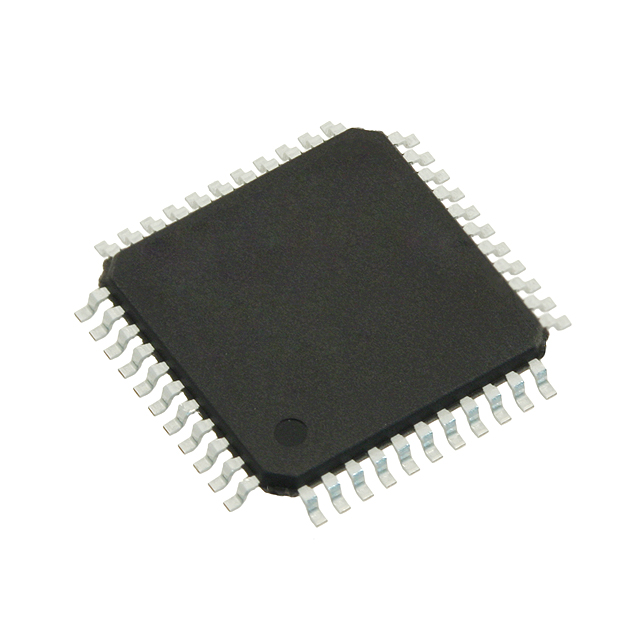

| 品牌: | XILINX/赛灵思 |

| 型号: | XC18V04VQ44C |

| 封装: | XILINX |

| 批号: | 最新批次 |

| 数量: | 2960 |

| 制造商: | Xilinx |

| 产品种类: | FPGA-配置存储器 |

| 存储类型: | EEPROM |

| 存储容量: | 4 Mbit |

| 最大工作频率: | 33 MHz |

| 工作电源电压: | 3.3 V |

| 最小工作温度: | 0 C |

| 最大工作温度: | + 70 C |

| 安装风格: | SMD/SMT |

| 封装 / 箱体: | VQFP-44 |

| 工作电源电流: | 25 mA |

| 系列: | XC18V04 |

| 电源电压-最大: | 3.6 V |

| 电源电压-最小: | 3 V |

| 单位重量: | 7.485 g |

Xilinx推出XC18V00系列系统内可编程配置PROM(图1)。该3.3V系列中的设备包括一个4兆比特、一个2兆比特、1兆比特和一个512千比特PROM,为Xilinx FPGA配置比特流的重新编程和存储提供了一种简单、经济高效的方法。当FPGA处于主串行模式时,它会生成一个配置时钟来驱动PROM。启用CE和OE后的短访问时间内,连接到FPGA DIN引脚的PROM data(D0)引脚上的数据可用。新数据在每个上升时钟沿之后的短访问时间内可用。FPGA生成适当数量的时钟脉冲以完成配置。当FPGA处于从串行模式时,PROM和FPGA由外部时钟计时。当FPGA处于主选择MAP模式时,FPGA会生成一个配置时钟来驱动PROM。当FPGA处于Slave Parallel(从并行)或Slave SelectMAP(从选择MAP)模式时,外部振荡器生成用于驱动PROM和FPGA的配置时钟。启用CE和OE后,PROM的data(D0-D7)引脚上的数据可用。新数据在每个上升时钟沿之后的短访问时间内可用。数据在CCLK的下一个上升沿被计时到FPGA中。自由运行振荡器可用于从并行或从SelecMAP模式。通过使用CEO输出来驱动以下设备的CE输入,可以级联多个设备。该链中所有PROM的时钟输入和DATA输出是互连的。所有设备都是兼容的,可以与该系列的其他成员级联,也可以与XC17V00一次性可编程串行PROM系列级联。

技术参数

技术参数